Half Adder is of the kind of basic digital circuit. Earlier there are various operations performed in Analog Circuits. After the discovery of digital electronics, similar operations are performed in it. The digital systems are considered to be effective and are reliable. Among the various operations, one of the most prominent operations is Arithmetic. It includes Addition, Subtraction, Multiplication, and Division. However, it is already known that it might be a computer, any electronic gadget like a calculator can perform mathematical operations. These operations are performed are consists of binary values.

This is possible by the presence of certain circuits in it. These circuits are referred to as Binary Adders and Subtractors. This type of circuits is designed for the binary codes, Excess-3 codes, and other codes as well. Further Binary Adders are classified into two types. They are:

- Half Adder and

- Full Adder

What is a Half Adder?

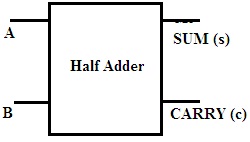

A digital electronic circuit that functions to perform the addition on the binary numbers is defined as Half Adder. The process of addition is denary the sole difference is the number system chosen. There exists only 0 and 1 in the binary numbering system. The weight of the number is completely based on the positions of the binary digits. Among those 1 and 0, 1 is treated as the largest digit and 0 as the smaller one. The Block diagram of this adder is

Half Adder

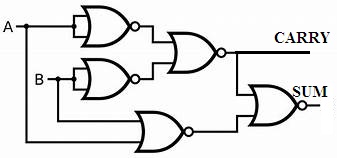

Half Adder Circuit Diagram

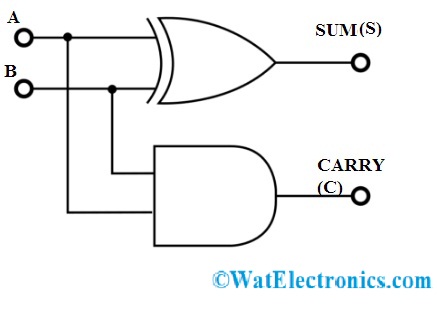

A half adder consists of two inputs and produces two outputs. It is considered to be the simplest digital circuits. The inputs to this circuit are the bits on which the addition is to be performed. The outputs obtained are the sum and carry.

Half Adder

The circuit of this adder comprises of two gates. They are AND and XOR gates. The applied inputs are the same for both the gates present in the circuit. But the output is taken from each gate. The output of the XOR gate is referred to as SUM and the output of AND is known CARRY.

Half Adder Truth Table

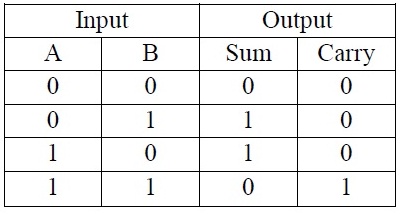

To obtain the relation of the output obtained to the applied input can be analyzed using a table known as Truth Table.

Half Adder Truth Table

From the above truth table the points are evident as follows:

- If A=0, B=0 that is both the inputs applied are 0. Then both the outputs SUM and CARRY are 0.

- Among two inputs applied if anyone the input is 1 then the SUM will b e1 but the CARRY is 0.

- If both the inputs are 1 then the SUM will be equal to 0 and the CARRY will be equal to 1.

Based on the inputs applied the half adder proceeds with the operation of addition.

Equation

The equation for this type of circuits can be realized by the concepts of Sum of Products (SOP) and Products of Sum (POS). The Boolean Equation for this type of circuits determines the relation between the applied inputs to the obtained outputs.

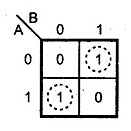

To determine the equation the k-maps are drawn based on the truth table values. It consists of two equations because two logic gates are used in it.

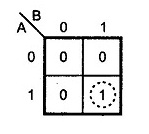

The k-map of the carry is

K-Map AND Gate

The output equation of CARRY is obtained from the AND gate.

C=A.B

The Boolean Expression for the SUM is realized by the SOP form. Hence the K-map for the SUM is

K-Map for Sum (XOR)

The equation determined is

S= A⊕ B

Applications

The applications of this basic adder are as follows

- To perform additions on binary bits the Arithmetic and Logic Unit present in the computer prefers this adder circuit.

- The combination of half adder circuits leads to the formation of the Full Adder circuit.

- These logic circuits are preferred in the design of calculators.

- To calculate the addresses and tables these circuits are preferred.

- Instead of only addition, these circuits are capable of handling various applications in digital circuits. Further, this becomes the heart of digital electronics.

VHDL Code

The VHDL code for the Half Adder circuity is

library ieee;

use ieee.std_logic_1164.all;

entity half_adder is

port(a,b: in bit; sum,carry:out bit);

end half_adder;

architecture data of half_adder is

begin

sum<= a xor b;

carry <= a and b;

end data;

FAQs

1. What do you mean by Adder?

The Digital Circuits whose sole purpose is to perform addition is known as Adders. These are the main components of ALU’s. Adders operate in addition to the various formats of numbers. The outputs of the adders are the sum and carry.

2. What are the Limitations of Half Adder?

The carry bit generated from the previous bit cannot be added is the limitation of this adder. To perform addition for multiple bits these circuits cant be preferred.

3. How to Implement Half Adder using NOR Gate?

The implementation of this type of adder can also be done by using the NOR gate. This is another Universal Gate.

Half Adder using NOR gates

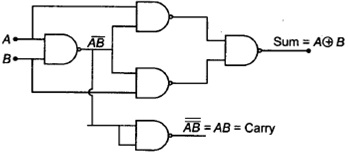

4. How to Implement Half Adder using NAND Gate?

The NAND gate is one of the kinds of universal gates. It indicates that any kind of circuit designing is possible by the use of NAND gates.

Half Adder

From the above circuit, the carry output can be generated by applying the output of one NAND gate to the input as other NAND gate. That is nothing but familiar to the output obtained from AND gate.

The output equation of SUM can be generated by applying the output of the initial NAND gate along with the individual inputs of A and B to further NAND gates. Finally, the outputs obtained by those NAND gates are applied to the gate again. Hence the output for the SUM is generated.

Please refer to this link to know more about Half Subtractor.

Please refer to this link to know more about Full Subtractor MCQs & Integrated Circuits MCQs.

Therefore the basic adder in the digital circuit can be designed by using various logic gates. But the multiple bits addition gets complicated and considered to be the limitation of the half adder. Can you describe which IC is used for the increment operation in any practical counters?