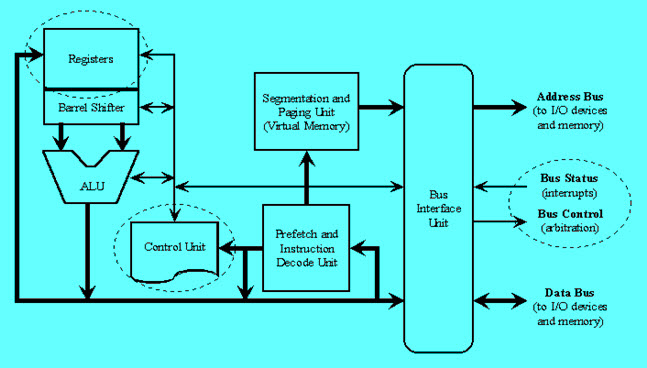

The architecture of the Central Processing Unit (CPU) operates the capacity to function from “Instruction Set Architecture” to where it was designed. The architectural design of the CPU is Reduced instruction set computing (RISC) and Complex instruction set computing (CISC). CISC has the capacity to perform multi-step operations or addressing modes within one instruction set. It is the CPU design where one instruction works several low-level acts. For instance, memory storage, loading from memory, and an arithmetic operation.

Reduced instruction set computing is a Central Processing Unit design strategy based on the vision that a basic instruction set gives great performance when combined with a microprocessor architecture. This architecture has the capacity to perform the instructions by using some microprocessor cycles per instruction. This article discusses the RISC and CISC architecture with appropriate diagrams. The hardware part of the Intel is named as Complex Instruction Set Computer (CISC), and Apple hardware is Reduced Instruction Set Computer (RISC).

What is RISC and CISC Architectures?

A complex instruction set computer is a computer where single instructions can perform numerous low-level operations like a load from memory, an arithmetic operation, and a memory store or are accomplished by multi-step processes or addressing modes in single instructions, as its name proposes “Complex Instruction Set ”.

A reduced instruction set computer is a computer that only uses simple commands that can be divided into several instructions which achieve low-level operation within a single CLK cycle, as its name proposes “Reduced Instruction Set ”

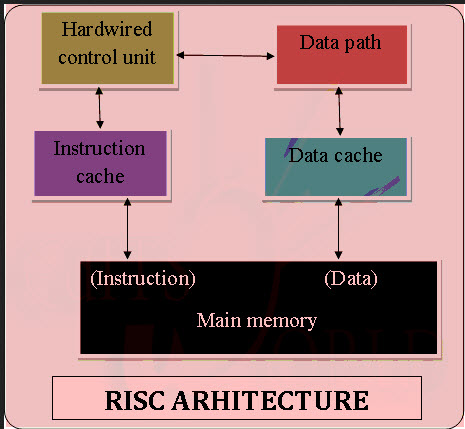

RISC Architecture

The term RISC stands for ‘’Reduced Instruction Set Computer’’. It is a CPU design plan based on simple orders and acts fast.

This is a small or reduced set of instructions. Here, every instruction is expected to attain very small jobs. In this machine, the instruction sets are modest and simple, which help in comprising more complex commands. Each instruction is about a similar length; these are wound together to get compound tasks done in a single operation. Most commands are completed in one machine cycle. This pipelining is a crucial technique used to speed up RISC machines.

RISC Architecture

Reduced Instruction Set Computer is a microprocessor that is designed to carry out few instructions at a similar time. Based on small commands, these chips need fewer transistors, which makes the transistors inexpensive to design and produce. The features of RISC include the following.

Please refer to this link to know more about Pipelining in Computer Architecture MCQs

- The demand for decoding is less

- Few data types in hardware

- General-purpose register Identical

- Uniform instruction set

- Simple addressing nodes

Also, while writing a program, RISC makes it easier by letting the computer programmer eliminate needless codes and stops wasting cycles.

Characteristics

The characteristics of RISC architecture include the following.

- Simple Instructions are used in RISC architecture.

- RISC helps and supports few simple data types and synthesizes complex data types.

- RISC utilizes simple addressing modes and fixed-length instructions for pipelining.

- RISC permits any register to use in any context.

- One Cycle Execution Time

- The amount of work that a computer can perform is reduced by separating “LOAD” and “STORE” instructions.

- RISC contains a Large Number of Registers to prevent various interactions with memory.

- In RISC, Pipelining is easy as the execution of all instructions will be done in a uniform interval of time i.e. one click.

- In RISC, more RAM is required to store assembly-level instructions.

- Reduced instructions need a less number of transistors in RISC.

- RISC uses the Harvard memory model means it is Harvard Architecture.

- A compiler is used to perform the conversion operation means converting a high-level language statement into the code of its form.

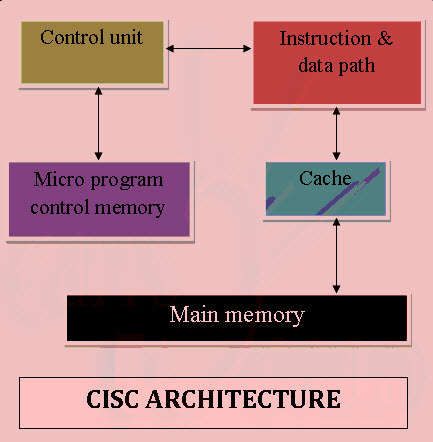

CISC Architecture

The term CISC stands for ‘’Complex Instruction Set Computer’’. It is a CPU design plan based on single commands, which are skilled in executing multi-step operations.

CISC computers have small programs. It has a huge number of compound instructions, which take a long time to perform. Here, a single set of instructions is protected in several steps; each instruction set has an additional than 300 separate instructions. Maximum instructions are finished in two to ten machine cycles. In CISC, instruction pipelining is not easily implemented.

CISC Architecture

The CISC machines have good acts, based on the overview of program compilers; as the range of innovative instructions are simply obtainable in one instruction set. They design compound instructions in a single, simple set of instructions.

They achieve low-level processes, which makes it easier to have huge addressing nodes and additional data types in the hardware of a machine. But, CISC is considered less efficient than RISC, because of its incompetence to eliminate codes which leads to wasting of cycles. Also, microprocessor chips are difficult to understand and program for, because of the complexity of the hardware.

- Instruction Set Architecture is a medium to permit communication between the programmer and the hardware. Data execution part, copying of data, deleting, or editing is the user commands used in the microprocessor, and with this microprocessor, the Instruction set architecture is operated.

- The main keywords used in the above Instruction Set Architecture are as below

Instruction Set: Group of instructions given to execute the program and they direct the computer by manipulating the data. Instructions are in the form – Opcode (operational code) and Operand. Where, the opcode is the instruction applied to load and store data, etc. The operand is a memory register where instruction is applied.

Addressing Modes: Addressing modes are how the data is accessed. Depending upon the type of instruction applied, addressing modes are of various types such as a direct mode where straight data is accessed or indirect mode where the location of the data is accessed. Processors having identical ISA may be very different in the organization. Processors with identical ISA and nearly identical organization is still not nearly identical.

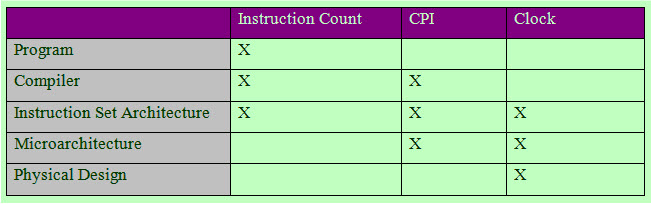

CPU performance is given by the fundamental law

![]()

Thus, CPU performance is dependent upon Instruction Count, CPI (Cycles per instruction), and Clock cycle time. And all three are affected by the instruction set architecture.

Instruction Count of the CPU

This underlines the importance of the instruction set architecture. There are two prevalent instruction set architectures

Examples of CISC Processors

IBM 370/168 – It was introduced in the year 1970. CISC design is a 32-bit processor and four 64-bit floating point registers.

VAX 11/780 – CISC design is a 32-bit processor and it supports many numbers of addressing modes and machine instructions which is from Digital Equipment Corporation.

Intel 80486 – It was launched in the year 1989 and it is a CISC processor, which has instructions varying lengths from 1 to 11 and it will have 235 instructions.

Characteristics

The characteristics of CISC architecture include the following.

- Instruction-decoding logic will be Complex.

- One instruction is required to support multiple addressing modes.

- Less chip space is enough for general purpose registers for the instructions that are 0operated directly on memory.

- Various CISC designs are set up with two special registers for the stack pointer, handling interrupts, etc.

- MUL is referred to as a “complex instruction

Comparison Between RISC and CISC

RISC stands for ‘Reduced Instruction Set Computer Whereas, CISC stands for Complex Instruction Set Computer. The RISC processors have a smaller set of instructions with few addressing nodes. The CISC processors have a larger set of instructions with many addressing nodes.

RISC vs CISC

Memory Unit

RISC has no memory unit and uses separate hardware to implement instructions. CISC has a memory unit to implement complex instructions

Program

RISC has a hard-wired unit of programming. CISC has a microprogramming unit

Design

RISC is a complex compiler design. CISC is an easy compiler design

Calculations

RISC calculations are faster and more precise. CISC calculations are slow and precise

Decoding

RISC decoding of instructions is simple. CISC decoding of instructions is complex

Time

Execution time is very less in RISC. Execution time is very high in CISC.

External memory

RISC does not require external memory for calculations. CISC requires external memory for calculations.

Pipelining

RISC Pipelining does function correctly. CISC Pipelining does not function correctly.

Stalling

RISC stalling is mostly reduced in processors. CISC processors often stall.

Code Expansion

Code expansion can be a problem in RISC whereas, in CISC, Code expansion is not a problem.

Disc space

Space is saved in RISC whereas in CISC space is wasted. The best examples of CISC instruction set architecture include VAX, PDP-11, Motorola 68k, And your desktop PCs on Intel’s x86 architecture, whereas the best examples of RISC architecture include DEC Alpha, ARC, AMD 29k, Atmel AVR, Intel i860, Blackfin, i960, Motorola 88000, MIPS, PA-RISC, Power, SPARC, SuperH, and ARM too.

SEMANTIC GAP

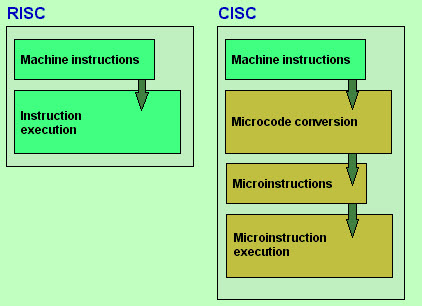

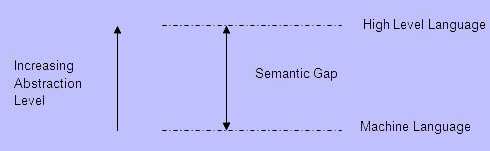

Both RISC and CISC architectures have been developed as an attempt to cover the semantic gap.

Semantic Gap

To improve the efficiency of software development, several powerful programming languages have come up, viz., Ada, C, C++, Java, etc. They provide a high level of abstraction, conciseness, and power. By this evolution, the semantic gap grows. To enable efficient compilation of high-level language programs, CISC and RISC designs are the two options.

CISC designs involve very complex architectures, including a large number of instructions and addressing modes, whereas RISC designs involve a simplified instruction set and adapt it to the real requirements of user programs.

CISC and RISC Design

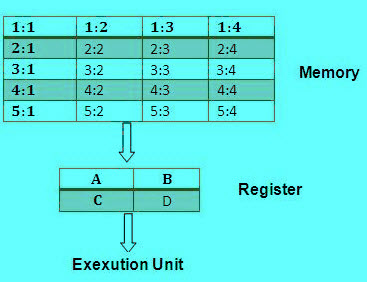

Multiplication of two Numbers in Memory

If the main memory is divided into areas that are numbered from row1:column 1 to row 5: column 4. The data is loaded into one of four registers (A, B, C, or D). To find multiplication of two numbers- One stored in location 1:3 and other stored in location 4:2 and store back result in 1:3.

Multiplication of Two Numbers

Applications of RISC and CISC

RISC is used in high-end applications like video processing, telecommunications, and image processing. CISC is used in low-end applications such as security systems, home automation, etc.

Advantages and Disadvantages

The advantages of RISC architecture include the following.

- RISC(Reduced instruction set computing)architecture has a set of instructions, so high-level language compilers can produce more efficient code

- It allows freedom of using the space on microprocessors because of its simplicity.

- Many RISC processors use the registers for passing arguments and holding the local variables.

- RISC functions use only a few parameters, and the RISC processors cannot use the call instructions, and therefore, use a fixed-length instruction that is easy to pipeline.

- The speed of the operation can be maximized and the execution time can be minimized.

A very less number of instructional formats, a few numbers of instructions, and a few addressing modes are needed.

The disadvantages of RISC architecture include the following.

- Mostly, the performance of the RISC processors depends on the programmer or compiler as the knowledge of the compiler plays a vital role while changing the CISC code to a RISC code

- While rearranging the CISC code to a RISC code, termed as a code expansion, will increase the size. And, the quality of this code expansion will again depend on the compiler, and also on the machine’s instruction set.

- The first level cache of the RISC processors is also a disadvantage of the RISC, in which these processors have large memory caches on the chip itself. For feeding the instructions, they require very fast memory systems.

The advantages of CISC architecture include the following.

- Microprogramming is an easy assembly language to implement, and less expensive than hard-wiring a control unit.

- The ease of microcoding new instructions allowed designers to make CISC machines upwardly compatible:

- As each instruction became more accomplished, fewer instructions could be used to implement a given task.

The disadvantages of CISC architecture include the following.

- The performance of the machine slows down due to the amount of clock time taken by different instructions will be dissimilar

- Only 20% of the existing instructions are used in a typical programming event, even though there are various specialized instructions in reality that are not even used frequently.

- The conditional codes are set by the CISC instructions as a side effect of each instruction which takes time for this setting – and, as the subsequent instruction changes the condition code bits – so, the compiler has to examine the condition code bits before this happens.

Please refer to this link to know more about Pipelining in Computer Architecture MCQs.

From the above comparison of RISC and CISC, finally, we can conclude that we cannot distinguish between RISC and CISC technology because both are apt at their precise application. Today, both RISC and CISC designers are doing all to get an edge on the competition. We hope that you have got a better understanding of this concept. Furthermore, any doubts regarding this concept, or to implement any electrical and electronic projects, please give your feedback by commenting in the comment section below. Here is a question for you, what are the different architectures available?