NMOS Fabrication Process

There are a huge number and assortment of fundamental fabrication steps utilized as a part of the generation of present-day MOS ICs. A similar procedure can be utilized for the planned of NMOS or PMOS or CMOS devices. The most commonly used material could be either metal or poly-silicon. The most regularly utilized substrate is mass silicon or silicon-on-sapphire (SOS). In order to keep a strategic distance from the nearness of parasitic transistors, varieties are acquired the systems that are utilized to isolate the devices in the wafer. The NMOS fabrication steps are as per the following.

NMOS Fabrication Steps

Using the fundamental processes, usual processing steps of the poly-Si gate self-aligning nMOS technology are discussed below. It can be superior understood by allowing for the fabrication of a single enhancement-type transistor. The step by step procedure of NMOS fabrication steps include the following

Step1:

Processing is passed on single crystal Si of high purity on which necessary P impurities is initiated as the crystal is developed. The diameter of such wafers are about 75-150 mm and 0.4 mm thick and they are doped with say boron to impurity absorption of 10 to power 15/cm3 to 10 to the power 16 /cm3.

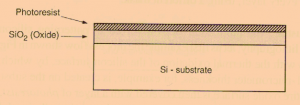

Step2:

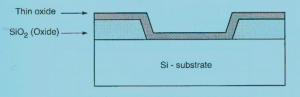

A SiO2 (silicon dioxide) layer normally 1 micrometer broad is grown all above the exterior of the wafer to guard the surface, performs as a barrier to the dopant through processing, and offers a generally protecting substrate on to which extra layers may be deposited and decorative.

![]()

Step 3:

The exterior (surface) is now enclosed with the photo oppose which is deposit onto the wafer and spun to an even distribution of the necessary thickness.

Step 4:

The photoresist coating is then uncovered to ultraviolet (UV) light through masking which describes those areas into which transmission is to take place as one with transistor channels. Suppose, for example, that those areas uncovered to UV radiations are polymerized, but that the areas necessary for diffusion are protected by the cover and remain unchanged.

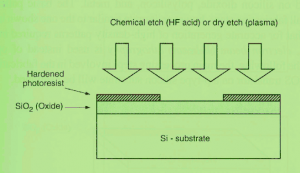

Step 5:

These regions are consequently readily fixed away together with the original silicon-di-oxide so that the surface of the wafer is uncovered in the window defined by the mask.

Step 6:

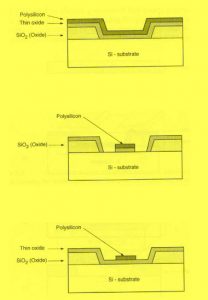

A thin layer of SiO2 (0.1 micro m typical) is grown over the chip surface after removing the remains of photoresist. Further, a gate structure is created by depositing polysilicon on the top of it. Factors like precise control of thickness, impurity concentration, and resistivity are necessary for the fabrication of fine pattern devices.

Step 7:

Further, the photoresist coating and masking allows the polysilicon to be patterned. After this, the thin oxide is removed to expose the areas. These areas are defused with n-type impurities by heating the wafer to a high temperature and passing the gas of desired n-type impurities to form the source and the drain.

Note: The polysilicon has an underlying thin oxide which acts as a mask during diffusion. This is called self-aligning.

Step 8:

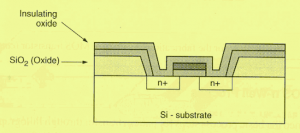

Again a thick oxide of SiO2 is grown over and then masked with photoresist. Now it is etched to expose selected areas of the polysilicon gate, drain and the source where connections are to be made.

Step 9:

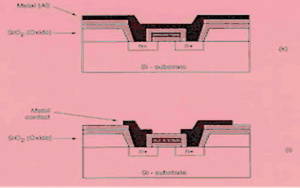

Now the whole chip has the deposits of the metal (aluminum) over its surface, typically to a thickness of 1micro m. This metal layer is masked and then etched to form the required interconnection pattern.

The above fabrication steps let only the arrangement of nMOS enhancement type transistors on a chip. But, if depletion type transistors are also to be created, one extra step is required for the arrangement of n-diffusions in the channel sections where depletion transistors are to be shaped. It engages one extra step that is, requires one extra mask to describe channel regions following a diffusion procedure using the ion implantation technique.

Please refer to this link to know more about CMOS and NMOS Technology.

For detailed information regarding the NMOS fabrication process. We hope that you have got a better understanding of this concept. Furthermore any queries regarding this concept or to implement any electronic projects please post your ideas and queries by commenting on the comment section below.